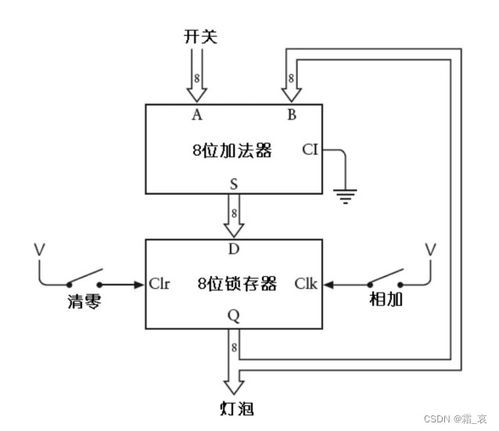

在《編碼:隱匿在計算機軟硬件背后的語言》第14章中,作者深入探討了邊沿觸發器與計數器這兩個構建現代計算機時序邏輯的核心組件。邊沿觸發器作為存儲單元的基礎,通過響應時鐘信號的上升沿或下降沿來鎖存數據,有效避免了電平觸發器中常見的空翻現象。這種特性使其成為寄存器、內存等存儲電路的理想選擇。計數器的設計則展現了時序邏輯的巧妙應用——通過級聯多個觸發器并配置反饋邏輯,可實現二進制、十進制或任意進制的計數功能。從頻率分頻器到程序計數器,從時鐘同步到狀態機控制,這些基礎模塊共同構成了計算機協調運作的時序框架。本章通過電路圖與波形分析的結合,揭示了數字系統中‘記憶’與‘時序’如何通過簡單的邏輯門與觸發器實現,為理解CPU流水線、緩存同步等高級概念奠定了實踐基礎。

邊沿觸發器與計數器 計算機時序邏輯的基石

更新時間:2026-04-10 21:29:48

如若轉載,請注明出處:http://www.lx1122.cn/product/39.html

PRODUCT

產品列表